1Learning Outcomes¶

Remember the adage: Load from memory, Store to memory.

Explain why an ISA needs to define instructions for accessing memory.

🎥 Lecture Video - Load from, Store to

Until 7:33[1]. Beyond that, there is a useful review of endianness, which we have covered in an earlier section.

Because registers are scarce, it is important to be cautious and reuse them as temporary storage. Generally, it is the job of an optimizing compiler to minimize register footprint. However, when we work with larger amounts of data, we have to “spill” out of the registers and over to memory.

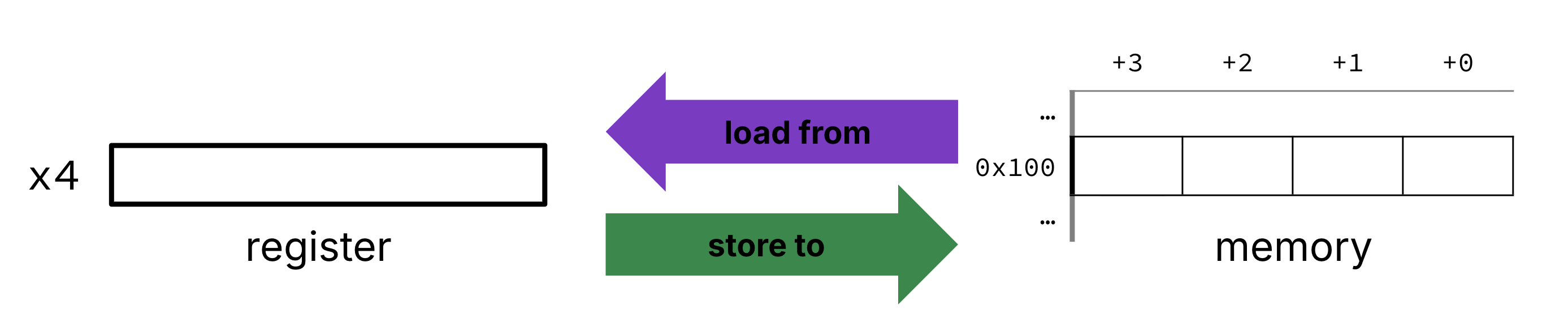

RISC-V defines instructions for accessing memory. Recall our basic computer layout (Figure 1). The processor communicates with memory by issuing addresses to read or write data:

Load from memory: Reading data from the memory into the processor.

Store to memory: Writing data from the processor to the memory.

2RISC-V is Load-Store¶

RISC-V is known as a load-store architecture[2]—referring to how it defines memory access and operations on data (Figure 1).

Figure 1:Load and store between register and memory.

RISC-V only permits operations on data in registers. Any operations on data from memory must involve multiple instructions:

Load in the data from memory into registers

Execute the operation on registers in the processor.

(if needed) Store the data back to memory.

RISC-V defines a set of load and store instructions for moving data between memory and registers. Let’s check these instructions out!

This lecture video starts with an amusing egg test. I personally believe it will help you grasp the concepts of the P&H textbook, but I haven’t tried it out yet.

Other models exist, often in CISC land. The x86 ISA permits arithmetic operations where one operand is in memory and the other is in a register.