Data Multiplexors By John Wawrzynek, with edits by Lisa Yan

1 Learning Outcomes ¶ Draw an n-bit wide, k-to-1 mux circuit.

Explain how the mux uses its control signal to select its output from a set of data inputs.

Last time we saw how to represent and design combinational logic blocks . In this section we will study a few special logic blocks; data multiplexors, a adder/subtractor circuit, and an arithmetic/logic unit.

2 The Mux ¶ A data multiplexor , commonly called a mux or a selector , is a circuit that selects its output value from a set of input values. Below are two mux circuits.

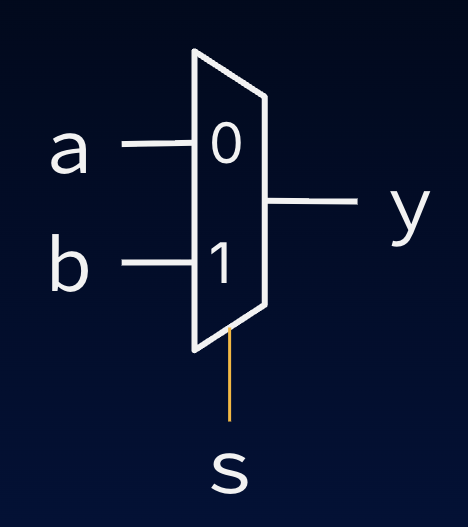

Both of these muxes have two data inputs and one output. Additionally, each mux has a special control signal labeled s, for select . The s signal is also input, but it is used to control which of the two input values is directed to the output.

Figure 1 1-bit wide , 2-to-1 mux circuit:

2-to-1 because it takes two data inputs a and b and outputs one of them.

It is 1-bit wide because all data signals (a and b) are 1-bit in width.

Notice, however, that the s signal is a single bit wide. This is because it must choose between the 2 inputs.

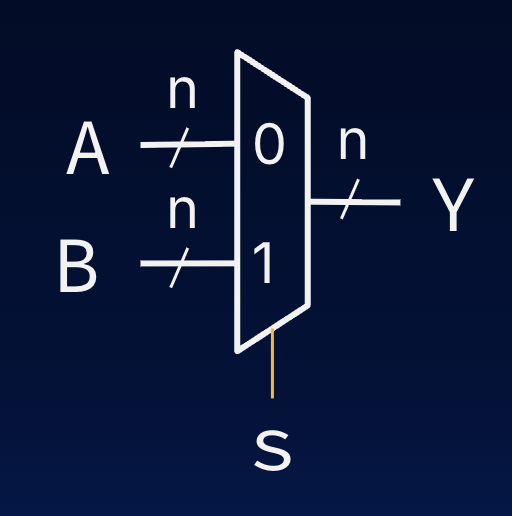

Figure 2 n-bit wide , 2-to-1 mux circuit:

2-to-1 because it takes two data inputs A and B and outputs one of them.

It is 1-bit wide because all data signals (A and B) are 1-bit in width.

The s signal is still a single bit wide because it must choose between the 2 inputs.

The function of, say, the 1-bit wide 2-to-1 mux

y = { a when s = 0 b when s = 1 \texttt{y} =

\begin{cases}

\texttt{a} & \text{when } \texttt{s} = 0 \\

\texttt{b} & \text{when } \texttt{s} = 1 \\

\end{cases} y = { a b when s = 0 when s = 1 To remind us of which value of s corresponds to which input, within the mux symbol we commonly label each input with its corresponding s value.

A mux is used whenever a circuit must choose data from multiple sources.

An n-bit wide N-to-1 MUX has N data inputs, 1 control input, and 1 output. The control input S selects between the other N inputs.

A 32-bit wide 4-to-1 MUX selects between __(1)__ input signals, each of which is __(2)__ bits wide. This mux circuit has __(3)__ selector bits.

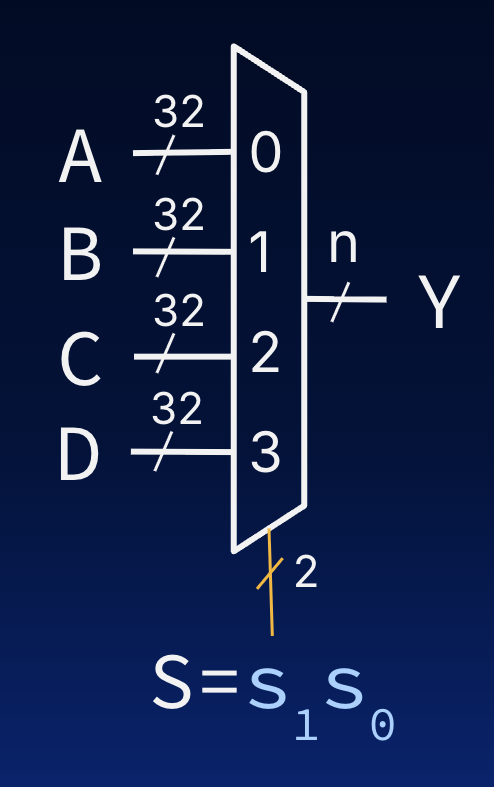

Figure 3: 32-bit 4-to-1 mux circuit.

4 input signals

32 bits wide

2 selector bits

Muxes find common use within the design of microprocessors, e.g., those that implement RISC-V.

3 MUX: Implementation ¶ In most applications, you will have access to a mux; you will not need to build your own from scratch. Nevertheless, it is good to remember that like all combinational logic blocks, the function of muxes can be described using a truth table and thereby implemented as a logic gate circuit.

Click to show the gate diagrams of two muxes: a 1-bit wide, 2-to-1 mux, and a 1-bit wide, 4-to-1 mux.

Table 1: Truth table for the 1-bit 2-to-1 mux in Figure 1 a, b, and control s), the truth table has 3 2 = 8 3^2 = 8 3 2 = 8

s ab y 0 00 0 0 01 0 0 10 1 0 11 1 1 00 0 1 00 0 1 01 1 1 10 0 1 11 1

To come up with the logic equation and the associated gate-level circuit diagram we can apply

the technique that we studied last chapter

y = a ‾ b ‾ c ‾ + a ‾ b ‾ c + a b ‾ c ‾ + a b c ‾ Sum of Products = a ‾ b ‾ ( c ‾ + c ) + a c ‾ ( b ‾ + b ) Distributivity = a ‾ b ‾ ( 1 ) + a c ‾ ( 1 ) Inverse (OR) x + x ‾ = 1 = a ‾ b ‾ + a c ‾ Identity (AND) x ⋅ 1 = x \begin{aligned}

y &= \overline{a} \overline{b} \overline{c} + \overline{a} \overline{b} c + a \overline{b} \overline{c} + a b \overline{c} && \text{Sum of Products} \\

&= \overline{a} \overline{b} (\overline{c} + c) + a \overline{c} (\overline{b} + b) && \text{Distributivity} \\

&= \overline{a} \overline{b} (1) + a \overline{c} (1) && \text{Inverse (OR) } x + \overline{x} = 1 \\

&= \overline{a} \overline{b} + a \overline{c} && \text{Identity (AND) } x \cdot 1 = x

\end{aligned} y = a b c + a b c + a b c + ab c = a b ( c + c ) + a c ( b + b ) = a b ( 1 ) + a c ( 1 ) = a b + a c Sum of Products Distributivity Inverse (OR) x + x = 1 Identity (AND) x ⋅ 1 = x Intuitively this result makes sense; When the control input, s, is a 0, the right hand side of the equation reduces to a, and when it is a 1, the expression reduces to b.

Figure 4: Gate diagram for a 1-bit 2-to-1 mux.

Often times we find the need to extend the number of data inputs of a multiplexor. For instance

consider a 4-to-1 multiplexor in Figure 5

Figure 5: A 1-bit wide 4-to-1 MUX.

e = { a when S = 00 b when S = 01 c when S = 10 d when S = 11 \texttt{e} =

\begin{cases}

\texttt{a} & \text{when } \texttt{S} = 00 \\

\texttt{b} & \text{when } \texttt{S} = 01 \\

\texttt{c} & \text{when } \texttt{S} = 10 \\

\texttt{d} & \text{when } \texttt{S} = 11 \\

\end{cases} e = ⎩ ⎨ ⎧ a b c d when S = 00 when S = 01 when S = 10 when S = 11 How would we come up with the circuit for this mux?

Approach 1 . We could start by enumerating the truth-

table—in this case the function has 4 single bit data inputs and one 2-bit wide control input, for a total of 6 single bit inputs. The truth table would have 26, or 64 rows. Certainly, a feasible approach. If we where to do this, we would end up with the following logic equation:

e = s 1 s 0 ‾ a + s 1 ‾ s 0 b + s 1 s 0 ‾ c + s 1 s 0 d e = \overline{s_1 s_0} a

+ \overline{s_1} s_0 b

+ s_1 \overline{s_0} c

+ s_1 s_0 d e = s 1 s 0 a + s 1 s 0 b + s 1 s 0 c + s 1 s 0 d Approach 2 . Another way to design the circuit is to base it on the hierarchical nature of multiplexing. We can build a 4-to-1 mux from three 2-to-1 muxes as shown in Figure 6 s 0 s_0 s 0 s 1 s_1 s 1

Figure 6: 4-to-1 multiplexor (MUX) circuit diagram.