1Learning Outcomes¶

Translate between B-Type assembly instructions and machine instructions.

Identify which instructions use PC-relative addressing and which use absolute addressing.

🎥 Lecture Video

1.1RISC-V Extension: 16-bit instructions¶

RISC-V Base ISA for RV32, RV64, RV128 all have 32-bit wide instructions. The “Base” ISA is extended by instruction extensions that do a range of items: general multiplication, different architecture support, etc.

One such extension is the 16-bit compressed extension extension, which accommodates variable-length instructions that are multiples of 16-bits in length. To proactively accommodate this and other extensions, the RISC-V Base ISA encodes half-word branch offsets, even when there are no 16-bit instructions in the base set.

In this course, we only focus on RISC-V processors with 32-bit instructions. Implications of this half-word branch offset:

Half of possible branch targets will be errors RISC-V conditional branches can only branch to instructions away from the PC.

2B-Type vs. I-Type, S-Type: Immediate Formats¶

Recall a core component of RISC-V design is to keep fields as consistent as possible across instruction formats. We have already seen how source/destination register fields rs1, rs2, and rs2 are consistent across formats, allowing clearer consistency of which registers to read and which to write.

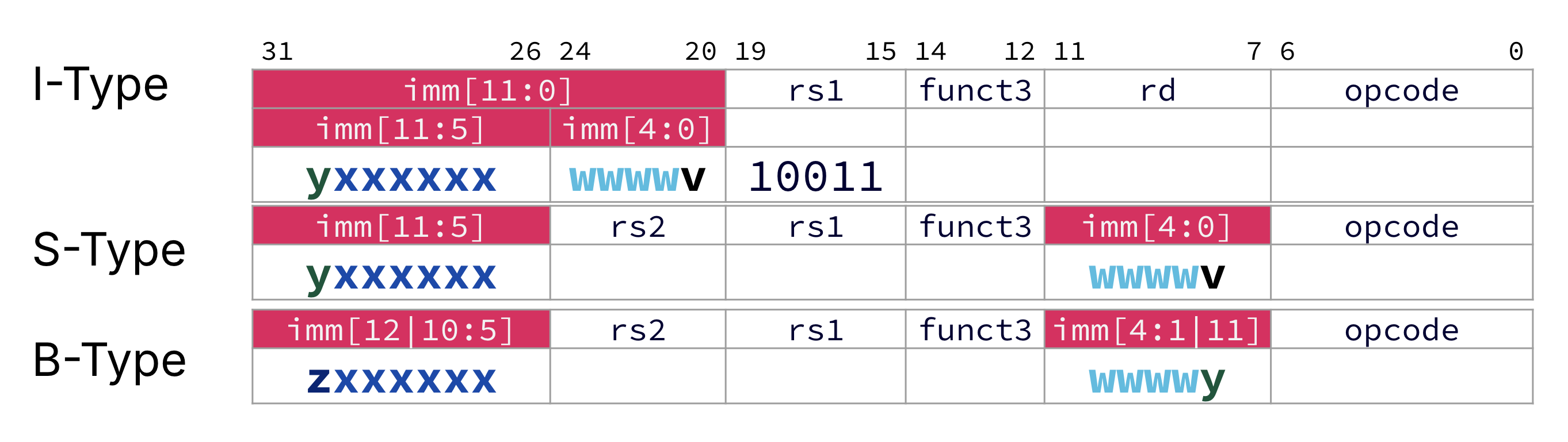

RISC-V also tries to keep bit positions of immediates consistent. The “swirling” of immediate bits in Figure 1 actually simplifies hardware design!

Figure 1:I-Type, S-Type, and B-Type instruction format comparison.

Observations:

Across I-Type, S-Type, B-Type, the instruction bit

inst[31]is always theimm’s sign bit.The 13-bit immediate of B-type has an

imm[0] = 0, so B-Type tries to keepimm[10:5],imm[4:1]in the same places as in the I-Type and S-Type, e.g., instruction bitsinst[26:30]andinst[8:11].S-Type, B-Type instruction formats have just two bits that change meaning:

The instruction bit

inst[31]is immediate bitimm[11]in S-Type andimm[12]in B-Type.The instruction bit

inst[7]is immediate bitimm[0]in S-Type andimm[11]in B-Type.