1Learning Outcomes¶

Write assembly to perform bitwise operations.

Understand why there are only three RISC-V bitshift operations:

sll,srl, andsra(and their immediate equivalentsslli,srli,srai).

🎥 Lecture Video

We recommend reviewing the C Bitwise Operations before continuing.

We have previously discussed that in RISC-V, operations determine “type,” i.e., how register contents are treated (see this table). Next, we will see how this concept applies to RISC-V’s instruction set for bitwise operations.

2Bitwise Operations¶

As before, bitwise operations are performed on n-bit operands one bit at a time.

The RV32I ISA provides instructions for common bitwise operations.[1]. Table 6 shows that most bitwise operations correspond to two instructions:

RISC-V: Register. Perform the bitwise operation on two register operands

rs1andrs2, and store the result in a destination registerrd.RISC-V: Immediate. Perform the bitwise operation on one register operand

rs1and an immediateimm, and store the result in a destination registerrd.

In Table 1 below, hover over each footnote to jump to the corresponding section on this page.

Table 1:RISC-V bitwise arithmetic instructions.

2.1The not pseudoinstruction¶

In RISC-V, bitwise NOT is a pseudoinstruction and corresponds to a bitwise XOR with the immediate -1:

NOT is XOR with -1.

| Pseudoinstruction | Name | Description | Translation |

|---|---|---|---|

not rd rs1 | bitwise NOT | R[rd] = ~(R[rs1]) | xori rd rs1 -1 |

Notes:

A bitwise NOT of the value

R[rs1]is defined as a bitwise inversion of all 32 bits of registerrs1.Recall from our discussion of XOR properties that for a single bit

x, the expressionx XOR 1(x ^ 1) invertsx.The immediate

-1has 32-bit two’s complement signed integer representation0b 1111 1111 1111 1111 1111 1111 1111 1111.

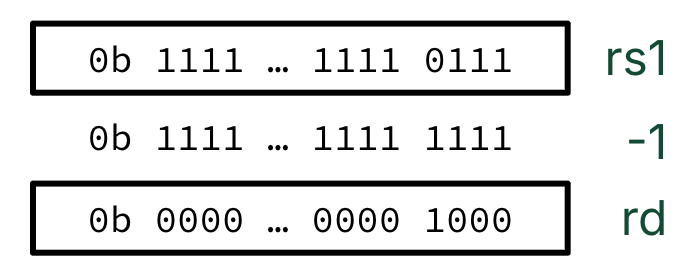

These three notes together explain Figure 1 below.

Figure 1:Add immediate instruction in RISC-V and C with negative values.

Show explanation

The source register

rs1has value0b 1111 1111 1111 1111 1111 1111 1111 0111.Destination register

rdhas value0b 0000 0000 0000 0000 0000 0000 0000 1000.By definition, this operation is both NOT (a bitwise inversion) and XOR with the 32-bit two’s complement representation of

-1.

2.2Shift left¶

Like all RISC-V arithmetic instructions, the left-shift operation sll must write all 32 bits of the destination register. Recall our discussion of the left shift operation: the expression x << n shifts the bits of x left by n bits, filling the n lower bits with zero. The sll operation therefore fills in these new bits with 0.

2.3Shift right¶

Recall our discussion of the right shift operation: the expression x >> n shifts the bits of x right by n bits, filling the n lower bits with zero or one. In C, this was determined by x’s type. In RISC-V, the instruction determines what the lower bits are filled in with

srl, or Shift Right Logical (srlifor immediate). “Zero-extend” and fill the upper bits with0. This instruction effectively interprets registerrs1’s contents as an unsigned integer. Read more in an earlier section.sra, or Shift Right Arithmetic (sraifor immediate). Fill in the upper bits with the sign bit of registerrs1. This instruction effectively interprets registerrs1’s contents as a signedinteger. Read more in an earlier section.

shift arithmetic: signed

3Other RISC-V arithmetic instructions¶

General multiplication is not included in the base RISC-V ISA but is specified as part of common RISC-V extensions. See the mul instruction on the RISC-V green card.

The circuitry for general multiplication is significantly more complicated than the bitwise left- and right-shift operations discussed above. For similar reasons, we do not discuss division, modulo, and floating point operations.[5]

4Practice¶

Show answer

B. 0x3400.

These instructions are the RISC-V translation of the C practice example when we discussed C bitwise operations. We recommend reviewing that first.

Each line, explained:

Write value

0x000034FFto registerx10.R[x10] << 0x10is0x34FF0000. Write this value to registerx12.R[x12] >> 0x8is0x0034FF00because the sign bit ofR[x12]is initially0.R[x12] & R[x10]is0x000034FF & 0x0034FF00is0x00003400. See Figure 1 from the C practice example.

See the full set of arithmetic instructions on the RISC-V green card.

See the

notpseudoinstruction.See shift left.

See shift right.

We encourage you to read the RISC-V unprivileged ISA for the M Extension and the F extension.